Intel's next-generation architecture overhaul! IPC performance soars, new APX instruction set

![]() 10/05 2024

10/05 2024

![]() 667

667

Fast Tech News, October 1st: According to reports, Intel is preparing a new P-core architecture codenamed "Panther Cove", which will significantly boost performance and introduce a new instruction set.

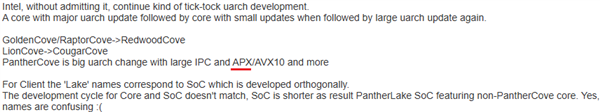

It is reported that Intel's current architecture design somewhat echoes the old Tick-Tock strategy, alternating between major and minor changes.

The current P-core architecture used in the Core Ultra 200 series is called Lion Cove, as is the case with Lunar Lake and Arrow Lake. It represents a significant transformation.

Its next generation is Cougar Cove, a relatively minor upgrade expected to be used in low-power Panther Lake and high-performance Nova Lake, i.e., the Core Ultra 300 series.

Next up is Panther Cove, which, if all goes as planned, will appear in the Razer Lake processor, part of the Core Ultra 400 series.

Panther Cove is another major architectural overhaul that will significantly boost IPC performance. Coupled with more advanced processes, both performance and energy efficiency should be impressive.

It will also introduce a new instruction set, APX, which stands for "Advanced Performance Extensions," an extension of the x86 instruction architecture.

APX adds more registers and numerous new features, such as doubling the number of general-purpose registers to 32, allowing compilers to store more data and instructions, including new reentry, storage, comparison, and test instruction formats, reducing the number of branch predictors and improving out-of-order execution efficiency.

APX will significantly enhance the general-purpose performance of CPUs without significantly increasing power consumption or chip area.

As for the purely 64-bit architecture X86S currently under development, it's still too early to tell when it will be released.